DSP-FPGA in einem Radarecho-Simulator

In einem von mir entwickelten Radarechosimulator für Bosch/Automotive habe ich ein Signalverarbeitungsmodul mit einem FPGA entwickelt.

Der Simulator wird in einer Closed-Loop betrieben und muss so die Echos in Echtzeit berechnen. Dadurch waren die Anforderungen an die Rechenleistung sehr hoch.

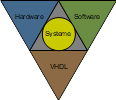

Realisiert wurde deswegen ein microcodierter Signalprozessor der Floatingpoint-Operationen u.a. auch Logarithmus ausführt und sich die Aufgabe mit einem handelsüblichen DSP teilt.

Darüberhinaus wurden in dem FPGA die Daten-Kommunikation, Kommandierung, Shared Memory und Bootlogik für den DSP integriert.